CPU Simulator/Compiler

CPU abstraction

CPU abstraction

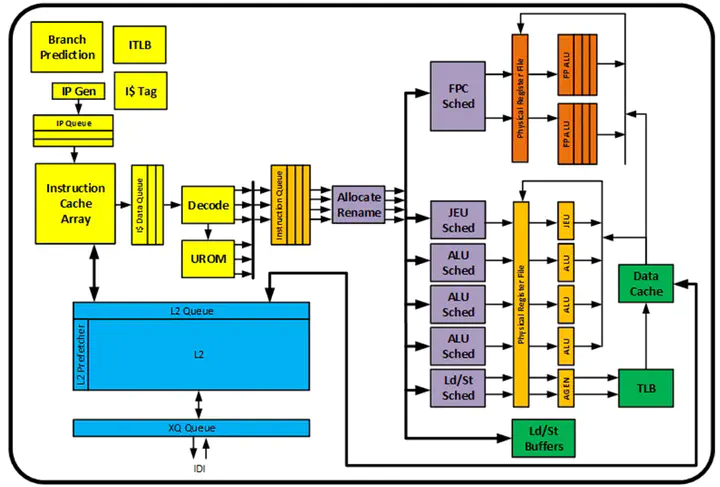

One part of the EIE second year Computer Architecture course was to develop, in C++, a CPU Simulator, based on the MIPS1 chip architecture. This virtual CPU was built in tandem with an automatic verification platform designed to exercise its capabilities. The deliverable had emphasis on rigorous memory management, data format encoding, including endianness as well as simulating exceptions and branch handling. The CPU and the verification platform followed a strictly defined Application Programming Interface (API) to make them portable and sustainable for potential future uses. It also enabled for my colleagues and me to test our work against each other’s frameworks, to ensure that our solutions were as rigorous as possible.

Reflecting on this coursework, it was a tremendously useful exercise that taught me in greater detail about memory management in C++ and improved my general programming skills. It also solidified my understanding of basic processor architectures, particularly Reduced Instruction Set Architectures. You can try my work for yourself at: Link.

Later in the course, I developed a compiler that took C89 code and compiled it down to the MIPS1 Instruction set. The output of this compiler would also be simulated using QEMU but could be ported to the CPU simulator. Once again, this compiler can be found at: Link.